### **FSM Sequences**

#### Radek Mařík

Czech Technical University

Faculty of Electrical Engineering

Department of Telecommunication Engineering

Prague CZ

November 18, 2025

### Outline

- Overview

- Distinguishing Sequence

- State Verifying Sequence

- State Characterizing Set

- 6 Homing Sequence

- **6** Synchronizing Sequence

### Outline

- Overview

- 2 Distinguishing Sequence

- State Verifying Sequence

- 4 State Characterizing Set

- 6 Homing Sequence

- 6 Synchronizing Sequence

## Set Theory and Strings

#### Definition 1.1

A **cardinality** of a set A is the number of elements of the set A. It is denoted |A|.

#### Definition 1.2

A **partition** (CZ rozklad) P of a set A is a set of nonempty subsets of A such that every element  $a \in A$  is in exactly one of these subsets, i.e., A is a disjoint union of the subsets.

#### String operations:

- ullet is the empty symbol, every extended alphabet  $X_{\epsilon}$  contains  $\epsilon$ ,

- $\bullet$   $|\epsilon|=0.$

- $x \cdot y$  means concatenation of strings (words) x and y. It can be also written as xy,

- |x| means the length of string (word) x.

### Finite State Machine

A finite-state machine is a sextuple  $(S, \Sigma, \Gamma, s_0, \delta, \lambda)$ , where

- S is a finite nonempty set of states,

- $\bullet$   $\Sigma$  is an input alphabet (a finite nonempty set of symbols),

- $\bullet$   $\Gamma$  is an output alphabet (a finite nonempty set of symbols),

- $s_0$  is an initial state,  $s_0 \in S$ ,

- $\delta$  is a state-transition function:  $\delta: S \times \Sigma \to S$ .

- $\lambda$  is an output function:  $\lambda: S \times \Sigma_{\epsilon} \to \Gamma_{\epsilon}$ .

#### Additional designations:

- $\Sigma^*$  is the set of all strings (words) over the input alphabet,

- $\Gamma^*$  is the set of all strings (words) over the output alphabet,

- Alphabet  $X^*$  always contains  $\epsilon$  and  $\forall x \in X^* : \epsilon \cdot x = x = x \cdot \epsilon$ .

- Thus  $X^*$  is always nonempty and it is also countable because X is countable.

### Input/Output Sequence

- An **input sequence** is a string of input symbols.

- An output sequence is a string of output symbols.

- An sequence experiment is an application of an input sequence to the given FSM from a given state and the output sequence is recorded.

- The main purpose of the experiment is a possibility to claim something about a given initial state or a final state.

- An experiment can be represented as a preset or adaptive sequence.

- The **preset form** is one input sequence.

- All symbols of the input sequence are applied and an output sequence is obtained.

- A single decision is based on the entire output sequence.

- The adaptive form is represented as a decision tree, where each internal node is an input symbol and edges to children are labeled by possible output symbols.

- The next input symbol depends on the observed previous output symbol.

- A FSM having a sequence in a preset form has always also an adaptive form of this sequence.

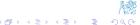

#### State Identification vs. State Verification

- A **state identification** sequence determines the initial state from which the sequence was applied if a representation of FSM is known.

- It also finds out the final state.

- Identification is usually based on a response of the machine, but some sequences are able to determine the final state regardless of the output.

- A state verification sequence verifies that the FSM was in a particular initial state which was not known before the experiment is performed.

- This can be achieved only by observing output and a representation of FSM must be known.

## FSM Sequences - Overview [Soul4]

November 18, 2025

### Outline

- Overview

- 2 Distinguishing Sequence

- State Verifying Sequence

- 4 State Characterizing Set

- 6 Homing Sequence

- 6 Synchronizing Sequence

## Distinguishing Sequence [Soul4]

#### Definition 2.1

A **distinguishing sequence** (DS) is an input sequence which distinguishes any two states according to the observed output.

- The application of a DS in each state provides no two identical output sequences.

- The final state is known after applying the DS.

- A distinguishing sequence is one of state identification sequences and also one of state verification sequences.

- If DS is applied in an unknown state, this state and also the final state is easily identified by the output.

- If the FSM is assumed to be in a certain state, the response after applying DS verifies whether the assumption was correct.

## Preset Distinguishing Sequence [Soul4]

#### Definition 2.2

A **preset distinguishing sequence** (PDS) (CZ přednastavená rozlišující sekvence) for a machine is an input sequence x such that the output sequence produced by the machine in response to x is different for each initial state, i.e.,  $\lambda^*(s_i, x) \neq \lambda^*(s_j, x)$  for every pair of states  $s_i$ ,  $s_j$ ,  $i \neq j$ .

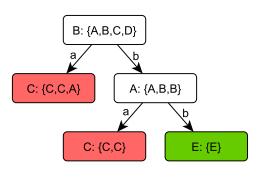

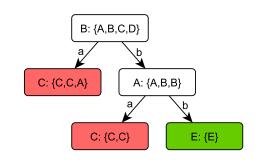

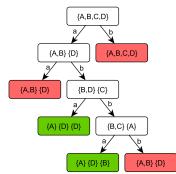

- The distinguishing sequences can be determined from a distinguishing tree.

- A distinguishing tree is a successor tree from which all minimal length distinguishing sequences can be derived.

### PDS algorithm I [DH94, Sou14]

- The distinguishing tree has an root node labeled with the set Q of all states of the machine.

- ② For each input  $a \in \Sigma$ , construct a branch from Q to a successor node which represents the set of all next states if the present state is in Q and the input a is applied. Group these states according to the outputs  $d \in \Gamma$  associated with the transition to the states. Each such group corresponds to the possible next states caused by transitions from Q with input a and output d.

- Obetermine terminal nodes of the tree according to the following rules:

- A node in which a state appears more than once in a group is a terminal node.

- A node which is identical to a node at an earlier level is a terminal node.

- Note that only groups that are formed by more than a single state should be compared.

- A node in which each group consists of a just single state is a termina

## PDS algorithm II [DH94, Sou14]

- If one or more nodes are terminal nodes defined by rule c) of step 3, the sequence of inputs corresponding to a path from the root node to such a terminal node is a distinguishing sequence for the machine. If all nodes terminate by rule a) or rule b), then the machine has no distinguishing sequence. If there are some nonterminal nodes in the tree, go to step 5.

- ullet For each nonterminal node  $Q_i$  and each input  $a \in \Sigma$ , construct a branch from  $Q_i$  to a successor node representing the next states of  $Q_i$  for input a. Group these states according to outputs, as in step 2, but do not group together any states generated by different subgroups of  $Q_i$ . Go to step 3.

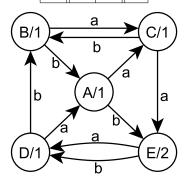

# PDS Example [Sou14]

# PDS Example Sequences [Soul4]

|   | aab | aba | abb | bab | bba |

|---|-----|-----|-----|-----|-----|

| Α | 122 | 111 | 111 | 121 | 121 |

| В | 111 | 112 | 112 | 122 | 111 |

| С | 221 | 221 | 221 | 111 | 112 |

| D | 222 | 211 | 211 | 211 | 212 |

### Outline

- Overview

- 2 Distinguishing Sequence

- State Verifying Sequence

- 4 State Characterizing Set

- 6 Homing Sequence

- Synchronizing Sequence

## State Verifying Sequence [LY94, Soul4

• A state verifying sequence (SVS) is also called *simple I/O* sequence [Hsi71] or *Unique Input Output sequence* [LY94].

#### Definition 3.1

A **state verifying sequence** of a state  $s \in S$  is an input sequence  $x \in \Sigma^*$ , such that the output sequence produced by the machine in response to x from any state other than s is different than that from s, i.e.,  $\lambda^*(s_i, x) \neq \lambda^*(s, x)$  for any  $s_i \neq s$ .

- When FSM could be in any particular state, just the SVS of this state is applied. Then the observed output sequence determines whether FSM was in the expected state or not.

- A union of state verifying sequences of all states in FSM is called states verifying set (SVSet) of FSM.

- A state does not have to have SVS and so SVSet is not defined.

### SVS Algorithm I [Sou14]

- The state distinguishing tree of state  $s \in S$  has an initial node labeled with the set Q of all states of the machine and state  $s \in Q$  is highlighted. For Moore machines the set Q contains only states with the same output symbol on  $\epsilon$  as state s has.

- ② For each input  $a \in \Sigma$ , construct a branch from Q to a successor node which represents the set of all next states if the state is in Q and the input a is applied and the output is equal to the output of transition from the fixed state  $s \in Q$ . In each successor node highlight the next state of the fixed state s.

- Oetermine terminal nodes of the tree according to the following rules. Note that the rules are listed in order of their testing.

- ullet A node in which the highlighted state s appears more than once in the label is a terminal node.

- A node which is identical to a node at an earlier level is a terminal node. Note that also highlighted states must be the same.

- A node with the fixed state s only is a terminal node.

## SVS Algorithm II [Sou14]

- If one or more nodes are terminal nodes defined by rule c) of step 3, the sequence of inputs corresponding to a path from the initial node to such a terminal node is a state verifying sequence for the fixed state s of the initial node.

- If all nodes terminate by rule a) or rule b), then the machine has no state verifying sequence for the state s.

- If there are some nonterminal nodes in the tree, go to step 5.

- For each nonterminal node  $Q_i$  and each input  $a \in \Sigma$ , construct a branch from  $Q_i$  to a successor node representing the next states of  $Q_i$  on input a.

- Eliminate states with different outputs than the fixed state  $s \in Q_i$  has on input a.

- Highlight a next state of s in each successor node, i.e. if s is fixed then  $\delta(s,a)$  is fixed.

- Go to step 3.

# SVS Example - Moore Machine [Soul4]

|   | а | b | $\epsilon$ |

|---|---|---|------------|

| Α | С | Е | 1          |

| В | С | Α | 1          |

| С | Е | В | 1          |

| D | Α | В | 1          |

| Е | D | D | 2          |

# SVS Example Sequences [Soul4]

|   | а | b | $\epsilon$ |

|---|---|---|------------|

| Α | С | Е | 1          |

| В | С | Α | 1          |

| С | Е | В | 1          |

| D | Α | В | 1          |

| Е | D | D | 2          |

|   | $\epsilon b$ | $\epsilon$ bb | $\epsilon$ a | $\epsilon$ aa | $\epsilon$ |

|---|--------------|---------------|--------------|---------------|------------|

| Α | 12           | 121           | 11           | 112           | 1          |

| В | 11           | 112           | 11           | 112           | 1          |

| С | 11           | 111           | 12           | 121           | 1          |

| D | 11           | 111           | 11           | 111           | 1          |

| Е | 21           | 211           | 21           | 211           | 2          |

### Outline

- Overview

- 2 Distinguishing Sequence

- State Verifying Sequence

- 4 State Characterizing Set

- 6 Homing Sequence

- Synchronizing Sequence

# State Characterizing Set [Soul4]

• For all states different from s there exists an input sequence  $x_k$ , such that the output sequences produced by the machine in response to  $x_k$  is different, i.e.,  $\forall s_i \neq s \; \exists x_k \in \Lambda_s : \lambda^*(s_i, x_k) \neq \lambda^*(s, x_k)$ .

#### Definition 4.1

A state characterizing set  $\Lambda_s$  of a state  $s \in S$  is a set of input sequences  $x_k \in \Sigma^*$ , such that the set of output sequences produced by the machine in response to all  $x_k$  from any state other than s is different than that from s, i.e.,  $\{\lambda^*(s_i,x_k) \,|\, x_k \in \Lambda_s\} \neq \{\lambda^*(s,x_k) \,|\, x_k \in \Lambda_s\}$  for any  $s_i \neq s$ .

- Each state of a reduced FSM has a state characterizing set (SCSet).

- Minimization of number of sequences in a state characterizing set can be proved to be NP-hard<sup>[HMU06]</sup> because Set cover problem which is NP-complete can be reduced polynomially to the minimization of sequence number problem.

## Characterization Set [Sou14]

- A characterizing set W is a set of input sequences  $x_k \in \Sigma^*$ , such that for each pair of states  $(s_i, s_j), s_i \neq s_j$ , there is sequence  $x_k \in W$  that distinguishes this pair, i.e.,  $\lambda^*(s_i, x_k) \neq \lambda^*(s_j, x_k)$ .

- W is also known as characterization set [Cho78].

- The characterizing set (CSet) can be obtained as union of SCSets of all states

#### [Sou14] SCSet Algorithm

- For each pair of states  $(s_i, s_i) \in S \times S$  apply each input  $a \in \Sigma$ . If on some a states  $s_i$  and  $s_j$  produce different output, store this input a as the shortest distinguishing sequence for pair  $(s_i, s_i)$ . For Moore machines distinguish pairs of states first by the empty string  $\epsilon$ .

- 2 For each pair  $(s_i, s_i)$  distinguished by the input sequence w in the previous step try to find an undistinguished pair  $(s_k, s_l)$  and an input a such that the pair of the next states  $(\delta(s_k, a), \delta(s_l, a)) = (s_i, s_i)$ . If there are such pair and input, store  $a \cdot w$  as a distinguishing sequence for the pair $(s_k, s_l)$

- 1 If some pair of different states is undistinguished, go to step 2. Otherwise create a characterizing set as a set of all distinguishing sequences stored in the previous steps. A state characterizing set of state s is a set of all sequences distinguished pairs  $(s, s_k)$ , where  $s_k \neq s$ , i.e.,  $\{w_k \in \Sigma^* \mid w_k \text{ distinguishes } (s, s_k) \in S \times S, s \neq s_k\}$ .

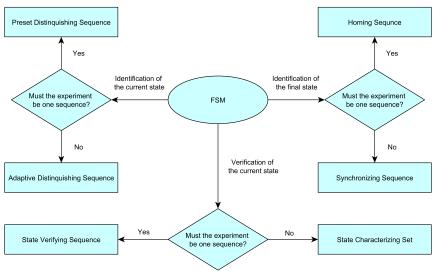

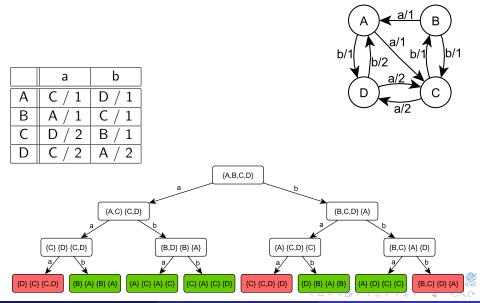

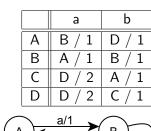

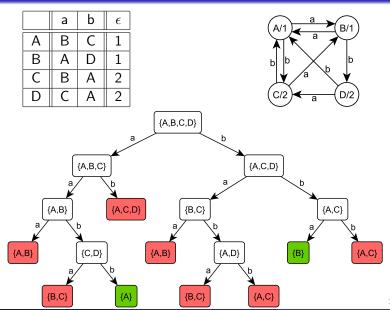

# SCSet Example - Mealy Machine [Soul4]

|   | а     | b     |  |

|---|-------|-------|--|

| Α | C / 1 | D / 1 |  |

| В | C / 1 | C / 1 |  |

| С | B / 2 | D / 1 |  |

| D | A / 2 | B / 1 |  |

|   | A   | В   | C  | D  | SCSet    |

|---|-----|-----|----|----|----------|

| Α | _   | bba | a  | а  | {a, bba} |

| В | bba | _   | а  | а  | {a, bba} |

| С | a   | a   | _  | ba | {a, ba}  |

| D | a   | a   | ba | _  | {a, ba}  |

### Outline

- Overview

- 2 Distinguishing Sequence

- State Verifying Sequence

- 4 State Characterizing Set

- 6 Homing Sequence

- 6 Synchronizing Sequence

# Homing Sequence [DH94, Soul4]

A homing sequence (HS) guides FSM to some specific states.

#### Definition 5.1

An input sequence x is said to be a **homing sequence** if the final state of the machine can be determined uniquely from the machine's response to x, regardless of the initial state. These final states of the machine are determined by observing the output sequence produced by applying a homing sequence to the machine.

- A homing sequence exists for all reduced FSM.

- If the current state of FSM is unknown, HS is applied and according to the output sequence a final state is determined.

- An adaptive form of sequence can rapidly reduce the length of homing sequence in some cases.

# HS algorithm [DH94, Sou14]

- The homing tree has an root node labeled with the set Q of all states of the machine.

- ② For each input  $a \in \Sigma$ , construct a branch from Q to a successor node which represents the set of all next states, if the present state is in Q and the input a is applied. Group these nodes according to outputs associated with the transitions to the states. Within any group, no state need be repeated.

- Oetermine terminal nodes in the tree according to the following rules:

- A node which is identical to a node at an earlier level is a terminal node.

- **1** A node in which each group is a single state is a terminal node.

- If one or more nodes are terminal nodes by rule b), a sequence of inputs from the root node to such a terminal node is a homing sequence. Note that all nodes cannot be terminal by rule a) since a homing sequence always exists. If there are some nonterminal nodes in the tree, go to step 5.

- ullet For each nonterminal node  $Q_i$  and each input a, construct a branch from  $Q_i$  to a successor node, representing the next state of  $Q_i$  for input a, grouping them by outputs and not grouping together states that are generated by different subgroups of  $Q_i$ . Go to step 3.

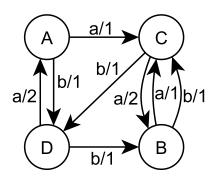

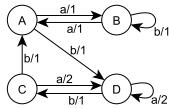

#### [Sou14] HS Example - Mealy Machine

# HS Example Sequences [Soul4]

|   | a     | b     |

|---|-------|-------|

| Α | B / 1 | D / 1 |

| В | A / 1 | B / 1 |

| С | D / 2 | A / 1 |

| D | D / 2 | C / 1 |

| initial | response | final | response  | final |

|---------|----------|-------|-----------|-------|

| state   | to $aba$ | state | to $abba$ | state |

| А       | 111      | Α     | 1111      | Α     |

| В       | 112      | D     | 1112      | D     |

| С       | 212      | D     | 2111      | В     |

| D       | 212      | D     | 2111      | В     |

### Outline

- 6 Synchronizing Sequence

## Synchronizing Sequence [DH94, Soul4]

- Some FSM can be synchronized to a particular state which means that FSM is in this state after applying a specific input sequence.

- The input sequence is called a synchronizing sequence (SS).

#### Definition 6.1

A **synchronizing sequence** is an input sequence which takes the machine to a unique final state independent of its initial state.

- This sequence has not an adaptive form because the decision is made regardless of the output.

- It is guaranteed that SS takes FSM into one state unlike HS which can take machine into more than one final state.

- SS has always at least the same length as HS

- FSM may not even have an SS.

- When output of FSM cannot be observed but a representation of FSM is known SS still can be used to determine the current state.

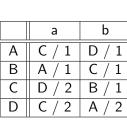

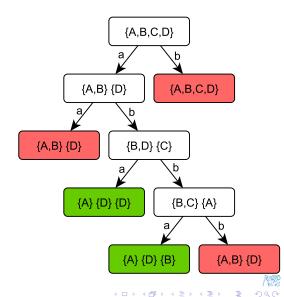

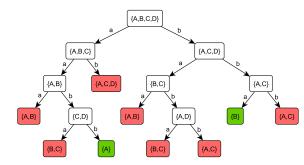

## SS algorithm | [DH94, Soul4]

- The synchronizing sequences can be found from a synchronizing tree which is a successor tree.

- The synchronizing tree is similar to the homing tree except that the states represented by a node are not grouped according to outputs since the final state must be determined independently of the output.

- The following steps are followed to build a synchronizing tree and derive all minimal length synchronizing sequences.

## SS algorithm II [DH94, Sou14]

- The synchronizing tree has an root node labeled with the set Q of all machine states.

- ② For each input  $a \in \Sigma$ , construct a branch from Q to a successor node which represents the set of all next states, if the current state is in Q and the input a is applied. Group these nodes disregarding the outputs associated with the transition to the states. Within the group, no state need to be repeated.

- Terminal nodes in the tree are determined according to the following rules:

- A node which is identical to a node at an earlier level is a terminal node.

- A node in which the group is a single state is a terminal node.

- If one or more nodes are terminal nodes by rule b), the sequence of inputs from the root node to such a terminal node is a synchronizing sequence. If all nodes are terminated by rule a), the machine has no synchronizing sequence. If there are some nonterminal nodes in the tree, go to step 5.

- **⑤** For each nonterminal node  $Q_i$  and each input a, construct a branch from  $Q_i$  to a successor node, representing the next states of  $Q_i$  for input a. Go to step 3.

### SS Example - Moore Machine [Sou

# SS Example Sequences [Soul4]

|   | a | b | $\epsilon$ |

|---|---|---|------------|

| Α | В | С | 1          |

| В | Α | D | 1          |

| С | В | Α | 2          |

| D | С | Α | 2          |

| initial | response | final | response  | final |

|---------|----------|-------|-----------|-------|

| state   | to $bba$ | state | to $aabb$ | state |

| Α       | 211      | В     | 1121      | Α     |

| В       | 211      | В     | 1121      | Α     |

| С       | 121      | В     | 1121      | Α     |

| D       | 121      | В     | 2121      | Α     |

### Summary

- Several sequences how to identify and verify states

- Distinguishing Sequence

- State Verifying Sequence

- State Characterizing Set

- Homing Sequence

- Synchronizing Sequence

## Competencies

- Define state identification and state verification.

- Define preset distinguishing sequence and describe its construction algorithm.

- Define state verifying sequence and describe its construction algorithm.

- Define state characterizing set and describe its construction algorithm.

- Define homing sequence and describe its construction algorithm.

- Define synchronizing sequence and describe its construction algorithm.

#### Literatura I

- [Cho78] Tsun S. Chow. Testing software design modeled by finite-state machines. Software Engineering, IEEE Transactions on, (3):178–187, 1978. Test: P.Z, W=characterization set Transfer and operation error, extra state Comparison: branch, switch and boundary-interior covers.

- [DH94] RG Deshmukh and GN Hawat. An algorithm to determine shortest length distinguishing, homing, and synchronizing sequences for sequential machines. In Southcon/94. Conference Record, pages 496–501. IEEE, 1994. Def and algorithms: DS, HS, SS - as successor tree.

- [HMU06] John E Hopcroft, Rajeev Motwani, and Jeffrey D Ullman. Introduction to Automata Theory, Languages, and Computation. Prentice Hall, 2006. Def: DFA, (eps-NIPA, RegEx, RegLang, CFL, Pushdown Automata, TM Undecidability, Intractable, P. (Co-)NP, NPC, (N)PSpace(-Complete), RP, ZPP.

- [Hsi71] E. P. Hsieh. Checking experiments ror sequential machines. *IEEE Transactions on Computers*, C-20(10):1152–1166, Oct 1971

- [LY94] David Lee and Mihalis Yannakakis. Testing finite-state machines: State identification and verification. Computers, IEEE Transactions on, 43(3):306–320, 1994. Def: state identification and verification Test whether FSM has a PDS is PSPACE-Complete There are FSM with exponential-long PDS as the shortest one Polynomial existence and constructing algorithm for ADS (based on Hopcroft minimization).

- [Sou14] Michal Soucha. Sequences of finite-state machines, BSc. thesis. Master's thesis, Department of Cybernetics, Faculty of Electrical Engineering, CTU, Prague, 2014. Department of Cybernetics, Faculty of Electrical Engineering, CTU, Prague.